# Advanced Design System 2002 Analog/RF User-Defined Models

February 2002

### Notice

The information contained in this document is subject to change without notice.

Agilent Technologies makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Agilent Technologies shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

#### Warranty

A copy of the specific warranty terms that apply to this software product is available upon request from your Agilent Technologies representative.

#### **Restricted Rights Legend**

Use, duplication or disclosure by the U. S. Government is subject to restrictions as set forth in subparagraph (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013 for DoD agencies, and subparagraphs (c) (1) and (c) (2) of the Commercial Computer Software Restricted Rights clause at FAR 52.227-19 for other agencies.

Agilent Technologies 395 Page Mill Road Palo Alto, CA 94304 U.S.A.

Copyright © 2002, Agilent Technologies. All Rights Reserved.

# Contents

| 1 | Building User-Compiled Analog Models                             |      |

|---|------------------------------------------------------------------|------|

|   | Background                                                       | 1-2  |

|   | Creating a New Model                                             |      |

|   | Starting a User-Compiled Model                                   |      |

|   | Defining the Model Parameters                                    | 1-4  |

|   | Creating the Model Symbol                                        | 1-7  |

|   | Setting Options                                                  | 1-8  |

|   | Creating the Code and Compiling the Model                        | 1-9  |

|   | Characteristics of User-Compiled Elements                        | 1-14 |

|   | Creating Circuit Elements Interface Definitions and Declarations | 1-16 |

|   | Series IV Functions                                              | 1-28 |

|   | Referencing Data Items                                           | 1-29 |

|   | Displaying Error/Warning Messages                                | 1-30 |

|   | Using Built-In ADS Linear Elements in User-Defined Elements      | 1-31 |

|   | Booting All Elements in a User-Defined Element File              |      |

|   | Porting Libra Senior to the ADS 1.0 Model Builder Interface      |      |

|   | Data Items                                                       | 1-33 |

|   | Default Units                                                    | 1-34 |

|   | Substrates/Built-In Models                                       | 1-34 |

|   | AEL Changes                                                      | 1-35 |

|   | Opening an Existing Model                                        | 1-35 |

|   | Deleting a User-Compiled Model                                   |      |

|   | Linking User-Compiled Models                                     |      |

|   | Managing Model Files                                             |      |

|   | Accessing Dynamically Loaded Devices                             | 1-41 |

| 2 | Creating Linear Circuit Elements                                 |      |

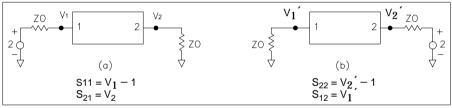

|   | Deriving S-Parameter Equations                                   | 2-1  |

|   | Deriving Y-Parameter Equations                                   |      |

|   | Coding a Linear Element                                          |      |

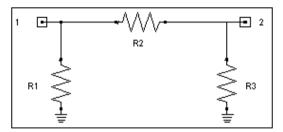

|   | Pi-Section Resistive Attenuator                                  |      |

|   | Transmission Line Section                                        |      |

|   | Deriving an S-Parameter                                          |      |

|   | Separating the Expressions                                       |      |

|   | Algorithms.                                                      |      |

|   | Applying a Problem to the Coaxial Cable Section                  |      |

|   | Calculating Remaining Expressions                                |      |

|   | Adding Noise Characteristics                                     |      |

|   |                                                                  |      |

#### 3 Creating Nonlinear Circuit Elements

|   | Requirements for Creating Nonlinear Elements<br>Linear Part<br>Nonlinear Part<br>AC Part                                    | 3-2<br>3-2<br>3-3 |

|---|-----------------------------------------------------------------------------------------------------------------------------|-------------------|

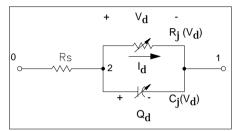

|   | User-defined P-N Diode Model<br>Defining a Nonlinear Element<br>Referencing Data Items<br>Displaying Error/Warning Messages | 3-5<br>3-17       |

| 4 | Creating Transient Circuit Elements                                                                                         |                   |

|   | Requirements for Creating Transient Elements                                                                                | 4-1               |

|   | Using Resistors, Capacitors, and Inductors                                                                                  |                   |

|   | Using Transmission Lines                                                                                                    | 4-3               |

|   | User-defined P-N Diode Model                                                                                                | 4-4               |

|   | Defining the Transient Device                                                                                               | 4-5               |

|   | Transient Analysis Function                                                                                                 | 4-6               |

|   | Referencing Data Items                                                                                                      |                   |

|   | Displaying Error/Warning Messages                                                                                           | 4-7               |

| 5 | Custom Modeling with Symbolically-Defined Devices                                                                           |                   |

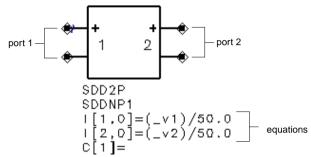

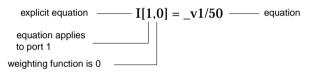

|   | Writing SDD Equations                                                                                                       | 5-3               |

|   | Port Variables                                                                                                              |                   |

|   | Defining Constitutive Relationships with Equations                                                                          | 5-4               |

|   | Explicit Representation                                                                                                     | 5-4               |

|   | Implicit Representation                                                                                                     | 5-5               |

|   | Explicit Versus Implicit Representations                                                                                    | 5-6               |

|   | Continuity                                                                                                                  |                   |

|   | Weighting Functions                                                                                                         |                   |

|   | Controlling Currents                                                                                                        |                   |

|   | Specifying More than One Equation for a Port                                                                                |                   |

|   | Using an SDD to Generate Noise                                                                                              |                   |

|   | Summary                                                                                                                     |                   |

|   | Adding an SDD to a Schematic                                                                                                |                   |

|   | Defining a Controlling Current                                                                                              |                   |

|   | Defining a Weighting Function                                                                                               |                   |

|   | SDD Examples                                                                                                                |                   |

|   | Nonlinear Resistor                                                                                                          |                   |

|   | Ideal Amplifier Block                                                                                                       |                   |

|   | Ideal Mixer                                                                                                                 |                   |

|   | Nonlinear Capacitors                                                                                                        |                   |

|   | Full Model Diode, with Capacitance and Resistance                                                                           |                   |

|   | Nonlinear Inductors                                                                                                         |                   |

|   | Controlling Current, Instantaneous Power                                                                                    | 5-34              |

|   | Gummel-Poon BJT                                         | 5-36 |

|---|---------------------------------------------------------|------|

|   | Examples Summary                                        | 5-43 |

|   | Modified Nodal Analysis                                 |      |

|   | Alternative Implementation of a Capacitor               | 5-47 |

|   | Error Messages                                          | 5-50 |

| 6 | Custom Modeling with Frequency-Domain Defined Devices   |      |

|   | Signal Models and Sources                               |      |

|   | Defining Sources                                        |      |

|   | The Frequency-Domain Defined Device                     |      |

|   | Retrieving Values from Port Variables                   |      |

|   | Defining Constitutive Relationships with Equations      |      |

|   | Continuity                                              |      |

|   | Specifying Carriers with the Freq Parameter             |      |

|   | Creating Output Harmonics                               |      |

|   | Trigger Events                                          |      |

|   | Output Clock Enables                                    | 6-17 |

|   | Accessing Port Variables at Trigger Events              |      |

|   | Delaying the Carrier and the Envelope                   | 6-19 |

|   | Miscellaneous FDD Functions                             | 6-20 |

|   | Defining Input and Output Impedances                    |      |

|   | Compatibility with Different Simulation Modes           |      |

|   | Components Based on the FDD                             | 6-22 |

|   | Adding an FDD to a Schematic                            |      |

|   | Defining Current and Voltage Equations                  |      |

|   | Defining Frequency Parameters                           |      |

|   | Defining Triggers                                       |      |

|   | Defining Clock Enables                                  | 6-27 |

|   | FDD Examples                                            | 6-28 |

|   | IQ Modulator                                            |      |

|   | Mixer                                                   |      |

|   | Sample and Hold                                         | 6-34 |

| 7 | User-Compiled Models                                    |      |

|   | Dialog Box Reference                                    |      |

|   | New User-Compiled Model dialog box                      | 7-1  |

|   | Circuit Type dialog box                                 | 7-2  |

|   | Open User-Compiled Model dialog box                     | 7-3  |

|   | User-Compiled Circuit Model, Parameters Tab             | 7-4  |

|   | User-Compiled Circuit Model dialog box (Model Code Tab) | 7-7  |

|   | Open File dialog box                                    | 7-10 |

|   | Save As dialog box                                      | 7-11 |

Code Options (Analog/RF Models) dialog box ...... 7-12

| Compile Options dialog box                           | 7-13 |

|------------------------------------------------------|------|

| User-Compiled Circuit Model dialog box (Options tab) | 7-15 |

| Delete User-Compiled Model dialog box                | 7-17 |

| Link User-Compiled Model dialog box                  | 7-18 |

| Link Options dialog box                              | 7-19 |

| Confirm Model File Not Created message               | 7-20 |

| Confirm Files Out-of-Synch message                   | 7-21 |

| File/Directory Management dialog box, UNIX           | 7-22 |

| File Management dialog box, PC                       | 7-23 |

| Directory Management dialog box, PC                  | 7-24 |

| ndex                                                 |      |

# Chapter 1: Building User-Compiled Analog Models

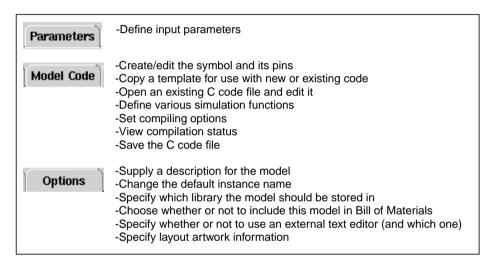

The Model Development Kit provides a graphical user interface that enables you to create your own circuit element models. Creating a model consists of three main steps:

- Defining the parameters whose values will be entered from the schematic

- Defining the symbol and the number of pins

- Writing the C-code itself

When appropriately coded, these elements can be used in linear, nonlinear (Harmonic Balance), transient, and Circuit Envelope simulations. The ADS Application Extension Language (AEL) provides the coupling between the parameters in the schematic design environment and the simulator. The Model Development Kit manages the AEL code generation completely. It also provides a template of the C code so all you need to do is add the relevant equations. Pin numbers and parameters are provided in easy-to-remember C macros and are automatically determined from the symbol drawing.

**Note** To use this tool, you must have the appropriate C++ compiler installed on your computer. For details, refer to the installation manual for your platform.

# Background

User-defined element models are implemented in ANSI-C code. The user-written code is then compiled and linked with supplied object code to make an executable program. This executable program serves as a replacement for the default circuit simulator program. While the equation and parametric circuit capabilities included in the circuit simulators can be used to effectively alter an element or network response through its parameters, the user-compiled model feature allows you access to state vector voltages that affect the model's response currents and charges.

The analysis code for user-compiled models can be written to influence its response depending on its parameters, stimulus controls, analysis type, and pin voltages. The user-defined code can make use of many built-in element models.

You supply the following information using ANSI-C code and AEL (either written by you or generated by the Model Development Kit interface):

- Definition (element names, number of pins, parameter list)

- Modeling functions (linear/nonlinear/transient/noise)

- Library and palette definitions

Note that although the user model is written in C, a C++ compiler is necessary for linking the entire program. The newly integrated elements can then be used in the same way as the built-in elements. A complete model can be developed, compiled and used in a simulation without exiting the schematic design environment.

**Note** This chapter shows an example on the PC and uses the back-slash ( $\setminus$ ) convention for file pathnames. On UNIX systems, the pathnames use the (forward) slash (/).

# **Creating a New Model**

This section uses an example to demonstrate the steps that are required to create a new analog user-compiled model using the Advanced Design System's Model Development Kit. The following procedures are shown:

- Starting a new model

- Defining the model parameters

- · Creating the model symbol and adding pins

- Writing and compiling the model

- Setting options

# Starting a User-Compiled Model

- 1. Verify that Analog/RF is the current design type.

- 2. From the Schematic window, choose Tools > User-Compiled Model > New User-Compiled Model.

- 3. Enter a name (in this example, *MyModel*). Click OK.

| - New U    | ser-Compile | d Model:3 |

|------------|-------------|-----------|

| Model Name |             |           |

| MyModel    |             |           |

|            |             |           |

| ОК         | Cancel      | Help      |

- 4. In the dialog box that appears, select the model type:

- Linear can have linear elements only

- Nonlinear can have both linear and nonlinear elements

Because this example model is a nonlinear diode (with two external pins and one internal node), select **Nonlinear** for the circuit type.

|   | Circuit Type:3 |  |  |

|---|----------------|--|--|

|   | 💠 Linear       |  |  |

| l | 🔷 Nonlinear    |  |  |

| ľ | OK Cancel Help |  |  |

| L |                |  |  |

5. Click **OK** and the User-Compiled Circuit Model dialog box appears.

#### **Defining the Model Parameters**

Use the Parameters tab to define input parameters. Each parameter must be specified by name in the Parameter Name field and a value type (integer, string, real, etc.) assigned to it.

**Hint** It is usually a good idea (but not required) to specify a default value in the Default Value field.

Optionally you can specify a Parameter Type (unit) and description, as well as a variety of parameter attributes. The Parameter Type controls the scale factor label that is displayed in the dialog box during subsequent editing in the Edit Component

Parameters dialog box. The text you enter in the Parameter Description field is displayed in the component parameter dialog box that appears when you edit a component/instance).

The remaining optional parameter attributes can be used as follows:

- *Display parameter on schematic*—defines whether or not the parameter appears on the schematic

- Optimizable—controls whether or not to allow this parameter to be optimized

- *Allow statistical distribution*—controls whether or not this parameter is allowed a statistical distribution when used in conjunction with the simulator's statistical features

**Note** Once the model is compiled and inserted in the design, these attributes cannot be modified.

If your parameters are similar to those a supplied component, you can copy and then modify them.

To copy the parameters of a supplied component:

- 1. Click Copy Parameters From.

- 2. When the library browser appears, select the appropriate library and component, in this example, *Devices-Diodes > Diode\_Model (PN-Junction Diode Model)*.

- 3. The parameter list is updated and can now be modified.

**Note** Copying parameters from a component will also copy the default symbol, which can then be modified as desired. The symbol can be seen when you click *Create/Edit Symbol and Pins* from the Model Code tab.

| Component Name: MyModel |                                            |  |

|-------------------------|--------------------------------------------|--|

| Parameters Model Code   | Options                                    |  |

| Select Parameter        | Edit Parameter                             |  |

| ls 🕹                    | Parameter Name                             |  |

| Rs                      | Iš                                         |  |

| N                       |                                            |  |

| Tt                      | Value Type                                 |  |

| Cjo                     | Real                                       |  |

| Vj                      |                                            |  |

| M                       | Default Value (e.g., 1.23e-12)             |  |

| Eg -                    | I                                          |  |

| Xti                     | Optional                                   |  |

| Kf                      |                                            |  |

| Af                      | Parameter Type                             |  |

| Fc                      | Current                                    |  |

| Bv                      |                                            |  |

| lbv                     | Parameter Description                      |  |

| Isr                     | Saturation Current, A, (default: 1.0e-14)] |  |

| Nr                      |                                            |  |

| lkf                     | Display parameter on schematic             |  |

| Nbv                     | X Optimizable                              |  |

| lbvl                    | •                                          |  |

| M                       | Allow statistical distribution             |  |

| Add Cut Paste           |                                            |  |

| Copy Parameters From    |                                            |  |

| ок                      | Apply Cancel Help                          |  |

# **Creating the Model Symbol**

Once the parameters are defined, the next step is to generate or create the schematic symbol (or modify the existing one if you used the *Copy Parameters From* option in the Parameters tab). This is done from the Model Code tab.

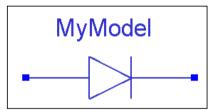

Click *Create/Edit Symbol and Pins* to switch to symbol view in the Schematic window. If you copied parameters from a supplied component (as in this example), the associated symbol will be there, otherwise a default symbol is generated, based on the number of ports on your design. Add any text or graphics as well as the proper number of external pins. The program will determine how many external nodes exist by the number of pins on the symbol page. You will be able to access the pins in your code via auto-generated macros. You can also modify the symbol graphics and number of pins at any time in the model generation process. Figure 1-1 shows the symbol after modification. The bounding box was deleted, external pins added, and text inserted.

Figure 1-1. Symbol after modification

When done defining the symbol, save the file and (optionally) close the window.

# **Setting Options**

Additional options can be set on the Options tab:

- A description for the model

- The library the model should be part of

- · Any associated layout artwork and macros

- An attribute to have the component counted in the Bill of Materials

- · Specifying an alternate text editor

By setting an alternate text editor you can use something other than the limited text editor accessed from the dialog box. Note that if you choose to use an external editor, it is up to you to save your files before compiling.

| User-Compiled Circuit Model:3                                   |        |  |

|-----------------------------------------------------------------|--------|--|

| Component Name: MyModel                                         |        |  |

| Parameters Model Code Options                                   |        |  |

|                                                                 |        |  |

|                                                                 |        |  |

|                                                                 |        |  |

| Component Description                                           |        |  |

| User-Compiled Model                                             |        |  |

| Component Instance Name Layout Artwork                          |        |  |

| MyModel                                                         |        |  |

| Library Name Synchronized                                       |        |  |

| My Circuit Library                                              |        |  |

| Include in Bill Of Materials                                    |        |  |

| Use External Text Editor                                        |        |  |

| hpeesofeedit                                                    |        |  |

| Note: Supported editors are emacs, hpeesofeedit, or notepad (PC | only). |  |

|                                                                 |        |  |

# Creating the Code and Compiling the Model

The code generation is done from the Model Code tab.

To set the desired options prior to generating:

Click **Code Options**. In the dialog box that appears, you can select those functions available, as well as set the value for the number of internal, nonlinear nodes. The *Transient* Function provides a field for *No. of internal nodes* for the transient topology. The field appears for both linear and nonlinear models. The *No. of nonlinear internal nodes* field displays only for nonlinear models.

| Code Options:3                     |

|------------------------------------|

| No. of nonlinear internal nodes    |

| Pre-Analysis Function              |

| Post-Analysis Function             |

| Noise Analysis Function            |

| Transient Function                 |

| 1 No. of capacitors                |

| i No. of infuctors                 |

| No. of transmission lines          |

| No. of internal nodes              |

| Use Convolution                    |

| Use Fix Transmission Line Function |

| OK Cancel Help                     |

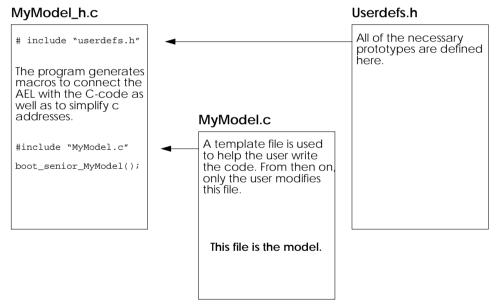

**Note** The program will generate a file (named *MyModel\_h.c* in this example) which has macros defined to either enable or disable the functions. This file is auto-generated for each compile, so you can modify these options if you decide to add another function. The user-edited file is not referenced in the Makefile, it is '#included' from the *MyModel\_h.c* file.

A template is provided to assist you in quickly creating your code. It is self-documenting and provides prototypes of all of the functions. (Note that functions are prototyped so that they at least return a value, but this does not guarantee that they will not cause simulation problems.)

To copy the template to your working model file:

- 1. Click **Create New Code Template**. In this example, the file will be called *MyModel.c*.

- 2. When the template code appears, edit as necessary to add the correct functionality for your model.

- 3. If using an external text editor, save the file.

Hint To edit an existing file, click Open File.

To set the compiling options prior to compiling:

Click **Compile Options**. Note that the current file is already in the *Object Files to be Linked* list box on the right-hand side. You can optionally select other models to be linked into the simulator. At this time you can also set the following options as desired:

• If compilation is successful, make executable

If the model compiles successfully, this option enables automatic linking. Because the linking can take a few minutes, you may not want to do this all the time.

• Recompile all out-of-date object files

Verifies whether the other models (not the current model) are out of date, and if so, recompiles them.

· Set debug flag on

When this option is selected, the appropriate flag is passed to the compiler to include the debug information in the object code. You will then be able to step through your code when the debugger is invoked. Refer to your debugger documentation for details.

| -                                      | Compile Options                  |  |  |

|----------------------------------------|----------------------------------|--|--|

| Active Projects                        |                                  |  |  |

| /a/new/hpsrmi/d1/users                 | s/staciat/ads/Documentation_pp 🗵 |  |  |

| Object Files in Project                | Object Files to be Linked        |  |  |

| MyModel (circuit)                      | /a/new/hpsrmi/d1/users/s         |  |  |

| PNDIODE (circuit)                      | /hfs/godot/d1/projects/Do        |  |  |

| U2PA (circuit)<br>U2PB (circuit)       |                                  |  |  |

| XLIN (circuit)                         | >>                               |  |  |

|                                        |                                  |  |  |

|                                        | «<                               |  |  |

|                                        |                                  |  |  |

|                                        |                                  |  |  |

|                                        |                                  |  |  |

| Select models to be linked             | Select models to be unlinked     |  |  |

| 🕱 If compilation is succes             | sful, make executable            |  |  |

| Recompile all out-of-date object files |                                  |  |  |

| 🕱 Set debug flag on                    |                                  |  |  |

|                                        |                                  |  |  |

| ΟΚ                                     | Cancel Help                      |  |  |

To compile the code:

Click **Compile Simulator**. The status is displayed in the Compilation Status pane. If the compile and link process was successful, a new simulator executable will have been generated in the current project directory. (If a prior executable existed, it will have been renamed.)

| Compilation Status        |                                   |

|---------------------------|-----------------------------------|

| Compile and link complete | Å                                 |

|                           | 4                                 |

|                           | Compile Simulator Compile Options |

| OK Apply                  | Cancel                            |

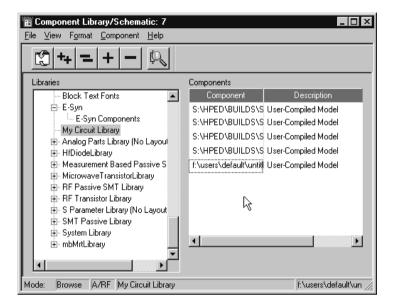

Once compiled, the model is immediately available in the design environment. From a Schematic window open the Library browser. The model can be found available in the *My Circuit Library* (unless you supplied a unique library name in the Options tab).

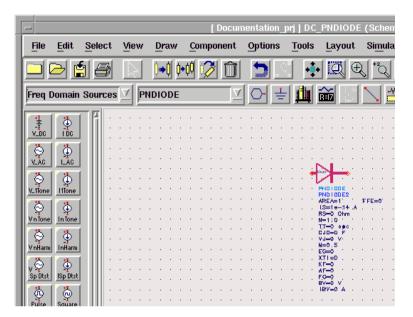

Select the component and place it on your schematic, just like any other built-in component.

# **Characteristics of User-Compiled Elements**

An unlimited number of user-defined elements in any number of C modules can be written, compiled and linked to your circuit simulator program. Linear elements can have up to 99 external pins, while nonlinear and transient elements can have any number of external pins and internal nodes.

An element without external pins is treated as a Model Form that has no electrical characteristics. Other elements can refer to this Model Form to obtain parameter values.

Element names and parameter keywords are limited to alphanumeric characters and the underscore character. Names cannot begin with a numeric character. In addition, a leading underscore is not recommended as this can interfere with the built-in variables. Any number of parameters of arbitrary type (integer, real, string or Model Form reference) are allowed for each element. A Model Form reference can refer to either a built-in or a user-defined Model Form.

For use in DC and frequency-domain simulations, an element can have either a linear or nonlinear model. Either type of element can have a transient model for use in a Transient simulation.

Linear and noise analysis responses of elements are computed in the frequency domain. The linear response can be computed either in complex scattering matrix or admittance matrix form. The noise response must be computed in complex current correlation matrix form. A user-defined linear element can call most any existing linear element to obtain its response.

Pre- and post-analysis entry points during program execution are provided to enable such calls and to perform special operations, such as data file reading and memory allocation/de-allocation.

Nonlinear element response is computed in the time domain at a sequence of time samples. Time-to-frequency transformations are computed in the circuit simulator engine and are transparent to the user. Element response is characterized by a set of instantaneous (nonlinear) currents out of each pin, nonlinear charges at each pin and their respective derivatives, all determined by applied pin voltages.

The user's computation functions cannot call other nonlinear elements for their responses. Element models with time-delay dependencies are supported.

Transient element response is computed in the time domain. Element response is characterized by a set of instantaneous (nonlinear) currents out of each pin, nonlinear charges at each pin and their respective derivatives, all as determined by applied pin voltages. Transient computation functions cannot call other elements (except for ideal resistors, capacitors, inductors and transmission lines) for their responses.

Convolution element response can be computed in two ways. One way is to use a linear model frequency response function so that the circuit simulation engine can compute the time-domain impulse response. Alternatively, specific nonlinear transient element response code can be used.

### **Creating Circuit Elements Interface Definitions and Declarations**

Interfacing to the simulator code requires the use of certain ADS defined public C symbols in user-defined element modules. The remainder of this chapter describes the supplied userdefs.h file that contains these symbols (macros, interface data structure typedefs, and function declarations). Note that the Model Development Kit interface will automatically generate most of these functions and that the header file will automatically be included.

Success or failure of a typical interface function call is determined by its return value, 1 for success and 0 for failure. Therefore, the 'boolean' typedef and these macros are provided. Although this boolean type is integer-valued, only TRUE and FALSE values should be associated with it.

```

#define FALSE 0

#define false 0

#define TRUE 1

#define true 1

typedef int boolean;

```

Four macros define the Boltzmann constant (Joules/Kelvin), the charge of an electron (Coulombs), the negative of absolute zero temperature (Celsius), and the standard noise reference temperature (Kelvin). The noise-current correlation parameters returned by an element's noise analysis function must be normalized to FOUR\_K\_TO--these parameters have admittance dimensions.

```

/* * define some physical constants */

#define BOLTZ   1.3806226e-23

#define CHARGE   1.6021918e-19

#define CTOK   273.15

#define NOISE_REF_TEMP   2 90.0 /* standard noise reference

temperature, in Kelvin */

#define FOUR_K_TO (4.0*BOLTZ*NOISE_REF_TEMP)

/* noise normalization 4kToB, B=1 Hz */

```

This macro obtains the number of items in an array definition at compile time.

#define siz(thing) (sizeof(thing)/sizeof(\*thing))

For clarity, an argument passed by reference can be prefixed by one of these macros in an ANSI function definition and prototype declaration.

```

#define IN /* input argument to function */

#define OUT /* output argument: modified/set by function */

#define INOUT /* argument used and modified by function */

#define UNUSED /* unused argument */

```

Linear response modeled in the frequency domain is complex, so the COMPLEX type is used for admittance (Y), scattering (S), and noise current-correlation parameters.

```

typedef struct

{

double real;

double imag;

}

COMPLEX;

```

Each element parameter has a specific type.

```

typedef enum

{

NO_data = -1,    /* unspecified */

REAL_data = 0,

INT_data = 1,

MTRL_data = 2,    /* for parameter referring to an instance */

STRG_data = 3,

COMPLEX_data = 4

}

DataTypeE;

```

Each element parameter definition consists of a keyword string and type.

```

typedef struct {

char *keyword;

DataTypeE dataType

}

UserParamType;

```

The parameter values of an item are obtained in an array of the UserParamData type. dataType is the discriminator tag to determine the actual value of the union. For example, if it is MTRL\_data, value.eeElemInst will refer to a substrate or model form.

```

typedef struct

{

DataTypeE dataType;

union

{

double dVal; /* for REAL_data */

int iVal; /* for INT_data */

void *eeElemInst; /* for MTRL_data */

char *strg; /* for STRG_data */

}value;

} UserParamData;

```

This type can be used specifically for 2-port elements if the conventional 2-port noise parameters are available.

```

typedef struct

{

double nFmin;   /* Noise Figure (dB) */

double magGamma;   /* |opt. source Gamma| */

double angGamma;   /* <opt. source Gamma (radians) */

double rnEff;   /* Effective normalized noise resistance */

double rNorm;   /* Normalizing resistance (ohms) */

} NParType;</pre>

```

Each user-element definition is of the UserElemDef type. The pre\_analysis function is useful for one-time operations such as parameter type checking, allocating memory, and reading data files. This routine is called for all types of analysis.

Note that a nonlinear or parametric subnetwork instantiation will be flattened (expanded) in the parent network. If there are two or more uses of a given subnetwork, each occurrence will result in the pre-analysis function (and post-analysis function) being called. The function must be written to properly manage such actions as reading data files and allocating memory.

The  $compute_y$  function must load the nodal admittance matrix parameters at frequency omega radians/sec into the passed yPar array. This function can call  $ee\_compute_y$  (described later) to use another element's admittance parameters.

The <code>compute\_n</code> function must load the normalized nodal noise current correlation parameters (Siemens, normalized to <code>FOUR\_K\_TO</code>) into the passed nCor array at frequency omega radians/sec and the element admittance parameters, <code>yPar</code>. It can call <code>ee\_compute\_y</code> (described later) to make use of another element's admittance and noise correlation matrices.

The post\_analysis function, called before processing a new circuit, is generally used for cleanup operations such as freeing memory or deleting temporary files. This function is called for all types of analysis. This function is called once for each occurrence of an element, so it must be written to properly manage this situation.

A nonlinear element must contain additional device information in a static area of type UserNonLinDef (described later); the pointer devDef must point to it.

The seniorInfo field is of arbitrary type, and can be used for any extra user-defined data/description that is of no concern to the simulator.

A transient response for an element can be defined in a structure of type UserTranDef (described later); the pointer tranDef must point to the structure. A transient response function can be defined for either a linear or nonlinear element.

```

typedef struct _UserElemDef UserElemDef;

struct _UserElemDef

{

char *name; /* Element name. Not to exceed 8 characters */

int numExtNodes; /* Number of external nodes, max. 20 for linear element */

int numPars; /* Number of parameters for this element */

UserParamType *params; /* parameter array */

```

/\* pre-analysis function: called after element item parsed successfully \*/

boolean (\*pre\_analysis)(INOUT UserInstDef \*pInst);

/\* Linear analysis function: called once for each new frequency point.

- \* Must return the item's admittance matrix in yPar array.

- \* NULL for nonlinear element \*/

```

boolean (*compute_y)(IN UserInstDef *pInst, IN double omega, OUT COMPLEX

*yPar);

```

/\* Linear noise-analysis function: called once for each new frequency point.

Must return the item's noise-current correlation admittance, normalized to

FOUR\_K\_TO in nCor array.

\* NULL if noiseless \*/

```

boolean (*compute_n)(IN UserInstDef *pInst, IN double omega, IN COMPLEX

*yPar, OUT COMPLEX *nCor);

```

/\* post-analysis: called before new netlist is parsed \*/

boolean (\*post\_analysis)(INOUT UserInstDef \*pInst);

```

UserNonLinDef *devDef; /* User's nonlinear device definition (NULL if

linear) */

struct _SeniorType *seniorInfo; /* Senior user defined type and data

(arbitrary) */

UserTranDef *tranDef; /* User's transient definition; NULL if none */

```

};

A nonlinear element response is characterized by the functions in the UserNonLinDef type.

numIntNodes is the number of nodes internal to the element. In its model, the element code must compute the contributions at all of its pins, which are ordered by external followed by internal pins. If a <code>UserTranDef</code> type is defined for the element, the <code>numIntNodes</code> in that structure must match this definition.

analyze\_lin must load only the linear part (complex admittances) of the nonlinear element in the frequency domain. Each admittance must be loaded by calling the primitive add\_lin\_y function. For a branch admittance between nodes (i, j), 4 calls are needed: +Y for (i, i), (j, j) and -Y for (i, j) and (j, i). analyze\_lin can use <code>ee\_compute\_y</code> to take advantage of pre-existing linear elements. <code>analyze\_nl</code> must compute and load the nonlinear response, using the element's pin voltages as input. The passed array pinVoltage contains instantaneous values; however, delayed voltage differences can be obtained using the <code>get\_delay\_v</code> function.

If P is the total number of pin voltages, formulate non-zero nonlinear current and charge at each pin n as follows:

rn (t) = f (v0 (t), v1(t),..., vP-1(t), vk(t-\*k), vl(t-\*l),...) where rn is the pin current or charge response,

\*k, \*l... are ideal delays, independent of the voltages. These responses and their derivatives with respect to voltage (nonlinear conductances, capacitances) must be computed and loaded using the add\_nl\_iq and add\_nl\_gc functions, respectively. Note that the derivatives help the simulator to converge to a solution, but do not affect the steady-state nonlinear response—therefore they may work even if not exact. However, under certain simulation conditions in-exact derivatives may cause convergence problems. However, for noise analysis they should be accurate, and for convergence they should be continuous.

In a linear simulation, a nonlinear element must contribute its small-signal linearized response; this is done through the <code>analyze\_ac</code> function. The linear part can be loaded by calling the element's <code>analyze\_lin</code> function. The linearized part is just the nonlinear conductances and capacitances computed above simply converted to admittances at angular frequency omega and loaded into the circuit matrix using <code>add\_lin\_y</code>.

Noise contribution of a nonlinear element in a linear simulation is added through the  $analyze_ac_n$  function. The linear and linearized noise correlation parameters are loaded using the primitive  $add_lin_n$  function. The linearized portion can include shot, flicker, and burst noise contributions.

The modelDef field is of arbitrary type and can be used for any extra user-defined nonlinear model data/description that is of no concern to the simulator.

```

typedef struct UserNonLinDef UserNonLinDef;

struct UserNonLinDef

{

int numIntNodes; /* # internal nodes of device */

/* Evaluate linear part (Y-pars) of device model */

boolean (*analyze lin)(IN UserInstDef *pInst, IN double omega)

/* Evaluate nonlinear part of device model:

nonlinear current out of each pin, nonlinear charge at each pin

* derivative (w.r.t. pin voltage) of each

* nonlinear pin current, i.e. nonlinear conductance q,

* derivative (w.r.t. pin voltage) of each

* nonlinear pin charge, i.e. nonlinear capacitance c

*/

boolean (*analyze nl)(IN UserInstDef *pInst, double *pinVoltage);

/* Evaluate small-signal AC model:

* compute total (linear+linearized) Y-pars of device

*/

boolean (*analyze_ac)(IN UserInstDef *pInst, IN double *pinVoltage, IN

double omega);

struct SeniorModel *modelDef; /* user-defined Senior MODEL (arbitrary) */

/* Evaluate bias-dependent linear noise model:

compute total (linear+linearized) noise-current correlation parameters

(normalized to FOUR_K_TO, siemens) of device

*/

boolean (*analyze ac n)(IN UserInstDef *pInst, IN double *pinVoltage,

IN double omega);

};

```

A transient response function can be defined for any element (linear or nonlinear) by defining the functions in the UserTranDef type shown.

numIntNodes is an arbitrary number of nodes internal to the element. In its model, the element must compute the contributions at all its pins, which are ordered and numbered (starting at zero) with the external pins first, followed by internal pins. If a UserNonLinDef type is defined for the element, the numIntNodes in that structure must match this definition.

Special routines are available to simplify the use of ideal resistors, capacitors, inductors, and transmission lines within a transient element. For the circuit simulator engine to perform the appropriate allocations, the number of these elements (except resistors) must be predefined using numCaps, numInds, and numTlines.

The analyze\_tr function must compute and load the instantaneous time domain response of the element, using the element's pin voltages as inputs. The passed array pinVoltage contains the instantaneous voltages at both the external and internal pins.

If P is the total number of pin voltages, formulate nonlinear current and charges at each pin n as follows:

rn (t) = f (v0(t),v1(t),..., vP-1 (t)) where rn is the current out of the pin or charge response. These responses and their voltage derivatives (nonlinear conductances and capacitances) must be computed and loaded using the  $add_tr_ig$  and  $add_tr_gc$  functions, respectively. Note that the derivatives are used to help converge to a solution, therefore the simulator may reach a solution even if they are not exact. However, under certain simulation conditions, inexact derivatives may cause convergence problems. Also, for convergence reasons, they should be continuous.

The fix\_tr function is called just before transient analysis begins. Its only purpose is to set up ideal transmission lines for the user. Using the add\_tr\_tline function, transmission line nodes and physical constants are defined. Once the transmission line is defined here, time-domain analysis of it is performed automatically without any further action by the user in the analyze\_tr function.

```

typedef struct UserTranDef UserTranDef;

struct _UserTranDef

{

numIntNodes; /* internal nodes of device */

int

int

numInds; /* number of explicit inductors */

numTlines; /* number of explicit transmission lines */

int

int

/* use linear response for convolution */

boolean useConvolution;

/* Evaluate transient model

* nonlinear currents out of each pin,

* nonlinear charge at each pin

* derivative (w.r.t. pin voltage) of each

* nonlinear pin current, i.e. nonlinear conductance q,

* derivative (w.r.t. pin voltage) of each

* nonlinear pin charge, i.e. nonlinear capacitance c

*/

boolean (*analyze tr)(IN UserInstDef *pInst, IN double *pinVoltage);

/* Pre-transient analysis routine used to allocate, compute and

* connect ideal transmission lines

* /

boolean (*fix_tr)(IN UserInstDef *pInst);

};

```

Each user-defined item placed in a design is represented in the ADS Simulator by the item type UserInstDef. All the fields, except seniorData, in an item are set up by ADS Simulator and must not be changed. seniorData can refer to arbitrary data and is meant to be managed by user code exclusively.

```

typedef struct _UserInstDef UserInstDef;

struct _UserInstDef

{

char *tag; /* item name */

UserElemDef *userDef; /* access to user-element definition */

UserParamData *pData; /* item's parameters */

void *eeElemInst; /* EEsof's element item */

void *eeDevInst; /* EEsof's nonlinear device item */

void *seniorData; /* data allocated/managed/used only by

Senior module (arbitrary) */

};

```

The get\_params function, below, loads the passed item eeElemInst parameter values into pData, which must be big enough to store all parameters. It is used to obtain referenced item (such as model substrate) parameters. Note that user-defined item parameters are already available in the UserInstDef.pData array, so there is no need to call get\_params for user item parameters. It returns TRUE if successful, FALSE otherwise.

extern boolean get\_params (IN void \*eeElemInst, OUT UserParamData \*pData);

These functions are useful to indicate program status in various stages of execution, such as during module boot-up, element analyses, and pre- or post-analysis.

```

extern void send_info_to_scn (IN char *msg); /* write msg to Status/

Progress window */

extern void send_error_to_scn (IN char *msg); /* write msg to Errors/

Warnings window */

```

In nonlinear analyses, for each set of independent input values (bias, frequency, power, or swept variable), ADS simulator attempts to find the steady state solution iteratively. In each iteration, nonlinear parts of all element items, including user-defined items, are evaluated. This function returns TRUE whenever the first iteration is in progress. It is most useful for parameter range checking, which is sufficient to do at the first iteration.

extern boolean first\_iteration (void);

This function returns TRUE whenever the circuit is being analyzed at the first point in a frequency plan. Note that this can happen many times in one simulation command for example, if there is another swept variable, or if an optimization/yield analysis is requested.

If a one-time-only operation is to be performed per circuit, the pre\_analysis function is recommended instead of this function.

extern boolean first\_frequency (void);

The function below computes the normalized complex noise correlation matrix for a passive element, given its Y-pars, operating temperature and number of pins.

```

extern boolean passive_noise (IN COMPLEX *yPar, IN double tempC, IN int

numNodes, OUT COMPLEX *nCor);

```

The function below computes the normalized complex noise correlation 2\*2 matrix for an active 3-terminal, 2-port element/network, given its Y-pars and measured noise parameters. Note that if numFloatPins is 2, the common (reference) third terminal is ground.

```

extern boolean active_noise (IN COMPLEX *yPar, IN NParType *nPar, int

numFloatPins, OUT COMPLEX *nCor);

```

The function below must be called (usually from nonlinear model's <code>analyze\_lin</code> and <code>analyze\_ac</code> procedure) to add the linear complex Y-parameter (iPin, jPin) branch contribution. This call must be done even for linear capacitive branches at DC (omega = 0), this will establish the Jacobian matrix entry location for subsequent non-zero harmonic omega.

```

extern boolean add_lin_y (INOUT UserInstDef *userInst, IN int iPin, IN int

jPin, IN COMPLEX y);

```

The function below must be called (from nonlinear model's <code>analyze\_ac\_n</code> function) to add the complex noise-current correlation term iNcorr (Siemens, normalized to FOUR\_K\_TO) from the (iPin, jPin) branch.

```

extern boolean add_lin_n (INOUT UserInstDef *userInst, IN int iPin, IN int

jPin, IN COMPLEX iNcorr);

```

The function below must be called (from nonlinear model's <code>analyze\_nl</code> function) to add the nonlinear conductance and capacitance contribution for the (iPin, jPin) branch.

```

extern boolean add_nl_gc (INOUT UserInstDef *userInst, IN int iPin, IN int

jPin, IN double g, IN double c);

```

The function below must be called (from nonlinear model's analyze\_nl function) to add the nonlinear current and charge contribution at the device pin iPin.

```

extern boolean add_nl_iq (INOUT UserInstDef *userInst, IN int iPin, IN

double current, IN double charge);

```

The function below can be called (from nonlinear model's analyze\_nl function) to get tau seconds delayed (iPin, jPin) voltage difference. Note that tau must not be dependent on device pin voltages--it is an ideal delay.

```

extern boolean get_delay_v (INOUT UserInstDef *userInst, IN int iPin, IN

int jPin, IN double tau, OUT double *vDelay);

```

Any transient support function that follows can use ground as a pin by using this special macro:

```

#define GND -1

```

The function below can be called (from the transient model's analyze\_tr function) to obtain the current time value, in seconds, of the transient analysis.

extern double get\_tr\_time (void);

The function below must be called (from the transient model's analyze\_tr function) to add the nonlinear conductance and capacitance contribution for the (iPin, jPin) branch.

```

extern boolean add_tr_gc (INOUT UserInstDef *userInst, IN int iPin, IN int

jPin, IN double g, IN double c);

```

The function below must be called (from the transient model's analyze\_tr function) to add the nonlinear current and charge contribution at the device pin iPin.

```

extern boolean add_tr_iq (INOUT UserInstDef *userInst, IN int iPin, IN

double current, IN double charge);

```

The function below can be called (from the transient model's <code>analyze\_tr</code> function) to add a resistor of <code>rval</code> Ohms between pin1 and pin2. The contribution of this resistor need not be included in the other calculated currents, charges and derivatives. If <code>rval</code> is less than 10<sup>-6</sup>, <code>rval</code> is set equal to  $10^{-6}$ .

```

extern boolean add_tr_resistor (INOUT UserInstDef *userInst, IN int

pin1,IN int pin2, IN double rval);

```

The function below can be called (from the transient model's <code>analyze\_tr</code> function) to add a capacitor of <code>cval</code> Farads between pin1 and pin2. The contribution of this capacitor need not be included in the other calculated currents, charges and derivatives. If <code>cval</code> is zero, an open circuit will exist between pin1 and pin2.

```

extern boolean add_tr_capacitor (INOUT UserInstDef *userInst, IN int

pin1,IN int pin2, IN double cval);

```

The function below can be called (from the transient model's analyze\_tr function) to add an inductor of lval Henries between pin1 and pin2. The contribution of this inductor need not be included in the other calculated currents, charges and derivatives. If lval is zero, a short circuit will exist between pin1 and pin2.

```

extern boolean add_tr_inductor (INOUT UserInstDef *userInst, IN int pin1,

IN int pin2, IN double lval);

```

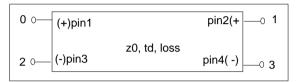

The function below can be called (from the transient model's fix\_tr function) to add an ideal transmission line. The impedance of the line is z0 Ohms and the propagation delay time of the line is td seconds. The loss parameter is used to describe the voltage attenuation on the line; a loss of 1.0 specifies a lossless line; a loss of 0.5 specifies an attenuation of 6 dB. The time domain simulation of this transmission line will be computed automatically with no further action by the user in the analyze\_tr function.

extern boolean add\_tr\_tline (INOUT UserInstDef \*userInst, IN int pin1, IN int pin2, IN int pin3, IN int pin4, IN double z0, IN double td, IN double loss);

The function below must be called by user-defined element code (possibly from a pre\_analysis function) that wants to use an element built in ADS. It returns a pointer to an allocated ADS item if successful, NULL otherwise. This pointer must be saved (possibly with the user-defined element item, in its seniorData field) and passed to ee\_compute\_y or ee\_compute\_n.

```

extern void *ee_pre_analysis (IN char *elName, IN UserParamData *pData);

```

These functions allow access to Advanced Design System elements for linear and noise analysis. Note that parameter data pData must be supplied in SI units, where applicable. They return TRUE if successful, FALSE otherwise. To determine parameter order, execute the simulator binary (hpeesofsim) using the -h flag and the name of the parameter (e.g.,  $\$HPEESOF_DIR/bin/hpeesofsim -h MLIN$ ).

```

extern boolean ee_compute_y (INOUT void *eeElemInst, IN UserParamData

*pData, IN double omega, OUT COMPLEX *yPar);

extern boolean ee_compute_n (INOUT void *eeElemInst, IN UserParamData

*pData, IN double omega, IN COMPLEX *yPar,OUT COMPLEX *nCor);

```

The function below must be called by user-defined element code (possibly from a post\_analysis function) for every ee\_pre\_analysis call to free memory allocated for the Advanced Design System item eeElemInst.

extern boolean ee\_post\_analysis (INOUT void \*eeElemInst);

This returns a pointer to the UserInstDef user-defined item if eeElemInst is indeed an item of a user-defined element, NULL otherwise.

extern UserInstDef \*get\_user\_inst (IN void \*eeElemInst);

The function converts between S- and Y-parameters. If direction is 0, it computes S-parameters into outPar using inPar as Y-parameters. If direction is 1, it computes Y-parameters into outPar using inPar as S-parameters. rNorm is the S-parameter normalizing impedance in ohms, and size is the matrix size. It returns TRUE if successful, FALSE otherwise.

extern boolean s\_y\_convert (IN COMPLEX \*inPar, OUT COMPLEX \*outPar, IN int direction, IN double rNorm, IN int size);

### **Series IV Functions**

The following C macros replace corresponding Series IV functions, which returned scale factors to convert a parameter value to SI. In ADS, parameter data are always considered to be in SI; hence these macros always return 1.0, and are meant only for Series IV compatibility.

```

#define get_funit(eeElemInst) 1.0 /* freq unit */

#define get_runit(eeElemInst) 1.0 /* resistance unit */

#define get_gunit(eeElemInst) 1.0 /* conductance */

#define get_lunit(eeElemInst) 1.0 /* inductance */

#define get_cunit(eeElemInst) 1.0 /* capacitance */

#define get_lenunit(eeElemInst) 1.0 /* length unit */

#define get_tunit(eeElemInst) 1.0 /* time unit */

#define get_angunit(eeElemInst) 1.0 /* angle unit */

#define get_curunit(eeElemInst) 1.0 /* current unit */

#define get_volunit(eeElemInst) 1.0 /* voltage unit */

#define get_watt(eeElemInst, power) (power) /* power unit */

```

### **Referencing Data Items**

A user-defined element parameter can be a reference to an ADS or a User-Defined item. Use the get\_params function to obtain the referenced item's parameters.

As an example, if you are creating a microstrip element and need an MSUB reference, the third parameter, for example, can be:

{"MSUB", MTRL\_data}

Then the array entry userInst->pData[2] will be such that pData[2].value.eeElemInst points to the referred MSUB item in the circuit. The MSUB parameters can then be obtained through a get\_params call:

get\_params(userInst->pData[2].value.eeElemInst, mData)

This will copy the MSUB parameters:

Er Relative dielectric constant.

Mur Relative permeability.

H (m) Substrate thickness.

Hu (m) Cover height.

T (m) r Conductor thickness.

Cond (Siemens/m) Conductor conductivity.

TanD Dielectric Loss Tangent.

Rough Conductor surface roughness.

into mData[0...7] locations. The mData array must be dimensioned large enough to hold all the referenced item's parameters. If a parameter value is not set or available, the `dataType' enum value will be NO\_data.

If the referenced item (using the third parameter again) is an item of a user-defined Data Item, then you can obtain a pointer to the user item as follows:

refInst = get\_user\_inst(userInst->pData[2].value.eeElemInst)

The function  $get\_user\_inst$  will return NULL if the passed argument is not a user-defined item.

# **Displaying Error/Warning Messages**

You can flag errors within a function in a user-defined element module and send messages to the Simulation/Synthesis panel. You can also write helpful status and debug messages to the Status/Summary panel. The following functions can be used for sending the message to respective locations:

- extern void send\_error\_to\_scn (char \*) writes message to Errors/Warnings panel

- extern void send\_info\_to\_scn (char \*) writes message to Status/Progress panel

The argument of these functions is a character pointer that is the error message string.

**Examples**:

send\_error\_to\_scn("divide-by-zero condition detected"); send\_info\_to\_scn("value of X falls outside its valid range");

#### **Using Built-In ADS Linear Elements in User-Defined Elements**

A user-defined element can call an ADS linear element to obtain the latter's COMPLEX Y and noise-correlation parameters. However, nonlinear devices, model items, and independent sources cannot be called in a user-defined element module. The relevant functions in the interface to support this feature are described below:

extern void \*ee\_pre\_analysis (char \*elName, UserParamData \*pData);

To allocate a pseudo item and do any pre-analysis processing such as data file reading, the user-defined element must first call this function. The second argument, UserParamData \*pData, must contain the data of correct type and in the order expected by the ADS element. The values must be in SI units where applicable. This function is usually called from the user-defined element's pre\_analysis function. It returns a pointer to an allocated ADS item if successful, NULL otherwise. This pointer must be saved (possibly with the user-defined element item, in its seniorData field) and passed to ee\_compute\_y or ee\_compute\_n.

```

extern boolean ee_compute_y (void *eeElemInst, UserParamData *pData,

double omega, COMPLEX *yPar);

```

The function below obtains N×N COMPLEX Y-parameters of the N-node (excluding ground) ADS element item in the user-supplied  $_{yPar}$  array at frequency omega radians/sec. It returns true if successful, False otherwise.

```

extern boolean ee_compute_n (void *eeElemInst, UserParamData *pData,

double omega, COMPLEX *yPar, COMPLEX *nCor);

```

The function below obtains the N×N COMPLEX Noise correlation matrix parameters, given *omega* and the N×N COMPLEX Y-pars. It returns TRUE if successful, FALSE otherwise.

```

extern boolean ee_post_analysis (void *eeElemInst);

```

This function must be called for each <code>pseudo</code> item created by each <code>ee\_pre\_analysis</code> call by the user-defined element. This frees up the memory allocated for the ADS item. It is usually called from the user-defined element's <code>post\_analysis</code> function. It returns <code>TRUE</code> if successful, <code>FALSE</code> otherwise.

### **Booting All Elements in a User-Defined Element File**

In order to keep the code modular, each user-defined element file can contain at most a single external/public symbol definition; this is the booting function, usually named <code>boot\_abc</code> for a module named <code>abc.c</code>:

boolean boot\_abc(void)

This function is called once per module—at program bootup. If the ModelBuilder interface is used, only one model per file is allowed. However, multiple files can be combined into one larger module by the user. The call to boot the module must be included in the self-documented <code>userindx.c</code> file at the appropriate location. The module's file name must be added to the <code>user.mak USER\_C\_SRCS</code> definition.

All user-defined elements in the module can be defined in a *static* (with module-scope) UserElemDef array, and booted by calling the provided function load\_elements from boot\_abc:

extern boolean load\_elements (UserElemDef \*userElem, int numElem);

If necessary, you can include code for technology/data file reading, as well as for automatic AEL generation, in the boot function.

# Porting Libra Senior to the ADS 1.0 Model Builder Interface

The ADS 1.0 Model Builder interface is designed to allow Series IV-Libra Senior models to be easily ported. Most models will require recompiling using the supplied makefiles. However, several features will require code modification if they were used:

- DataItems

- Default Units

- Substrates

- Calls to built-in elements

### **Data Items**

The Data Item is replaced by references to an AEL expression, or equation. Users can still access default values, however, the '\*' value is no longer supported and must be replaced by references to built-in values. For example, the Series IV Data Items can be set via comparable VAR expressions:

\_DEFAULT\_TEMP = 290.15

\_DEFAULT\_REF = 50

Instead of using the '\*' value to indicate the default, the parameter should be left blank. If the value on the schematic is set to blank the simulator defaults to the Series IV default values:

| TEMP  | Temperature                     | TEMP = 27 C       |

|-------|---------------------------------|-------------------|

| RREF  | Reference resistance            | R = 50 Ohm        |

| TAND  | Dielectric loss tangent         | TAND = 0          |

| PERM  | Permeability & Mag loss tangent | MUR = 1; TANM = 0 |

| SIGMA | Dielectric conductivity         | SIGM = 0          |

# **Default Units**

The concept of Default Units is not used in ADS. Instead, each parameter on a component can have a scale factor. The simulator's parsing utility replaces the parameter value+scale factor with the proper number (e.g., 1.23GHz is supplied to the user's program as 1.23e9). Any calls to  $get\_unit$  functions are still supported; they merely return a value of 1.

Note that the scale label is ignored:

Resistance = 100 kOhm = 100 \* 1e3 = 100 kBricks = 100 kHz

All calls to any of the units functions are all equivalent (the user's code will receive a value of le5).

### Substrates/Built-In Models

The substrate use model has changed considerably in ADS and requires users to modify their calls to any substrate components. Certain parameters have been moved from Data Items to the instance, others to the substrate component. The order and name of the parameters has also changed. Conductivity is specified instead of resistivity.

User calls to built-in models may also have changed, depending on the element. Users will have to reconfirm parameter ordering.

To determine parameter order, execute the simulator binary (hpeesofsim) using the -h flag and the name of the parameter (e.g., \$HPEESOF\_DIR/bin/ *hpeesofsim -h MLIN*).

# **AEL Changes**

Series IV AEL may require substantial modification. For example, AEL references to Series IV forms (rvopt, etc.) should be changed to 'StdFormSet.' It may be expedient to use the Model Development Kit to generate the AEL file rather than edit a Series IV file.

```

create_item("U2PA","User-Compiled Model","U2PA",16,-1,NULL,"Component

Parameters","","%d:%t%#%44?0%:%31?%C%:_net%c%;%;%e%b%r%8?%29?%:%30?%p%:%k%?

[%li]%;=%p%;%;%e%e%;","U2PA",3,NULL,64,

create_parm("R1","Pin 1 to GND Resistance ",68608,"StdFormSet",-1,

prm("StdForm","50")),

create_parm("R2","Pin 1 to Pin 2 Resistance",68608,"StdFormSet",-1,

prm("StdForm","50")),

create_parm("R3","Pin 2 to GND Resistance",68608,"StdFormSet",-1,

prm("StdForm","50")))

```

# **Opening an Existing Model**

To work on an existing user-compiled model, open the project where the model exists. Use the menu command Tools->Open User-Compiled Model. Select the model from the browser.

# **Deleting a User-Compiled Model**

To permanently delete an existing user-compiled model, open the project where the model exists. Use the menu command Tools->Delete User-Compiled Model. Select the model to be deleted from the list. Click *Apply* to delete the model and leave the dialog box active, or click *OK* to delete the model and dismiss the dialog. Click *Cancel* to dismiss the dialog without deleting the model.

| Г |    |                                                                                                                                 |  |  |

|---|----|---------------------------------------------------------------------------------------------------------------------------------|--|--|

|   | -  | Delete User-Compiled Model:2                                                                                                    |  |  |

|   | Ac | Active Projects                                                                                                                 |  |  |

|   | _  | /hfs/godot/d1/projects/Documentation_prj/netw( _/                                                                               |  |  |

|   | м  | Models in Project                                                                                                               |  |  |

|   |    | yModel (circuit)                                                                                                                |  |  |

| I |    | PNDIODE (circuit)                                                                                                               |  |  |

| 1 |    | 2PA (circuit)                                                                                                                   |  |  |

| I |    | 2PB (circuit)                                                                                                                   |  |  |

|   | X  | LIN (circuit)                                                                                                                   |  |  |

|   |    |                                                                                                                                 |  |  |

|   |    |                                                                                                                                 |  |  |

|   |    |                                                                                                                                 |  |  |

|   |    |                                                                                                                                 |  |  |

| I |    |                                                                                                                                 |  |  |

|   | S  | elect the models to be deleted                                                                                                  |  |  |

|   |    | ote: You will need to recompile any models that linked in the<br>eleted model. Use Tools>Link User-Compiled Model to recompile. |  |  |

|   |    | OK Apply Cancel Help                                                                                                            |  |  |

The program prompts you for confirmation before deleting.

# Linking User-Compiled Models

Previously compiled user models can be linked without recompiling. Move the model files into the projects networks directory. Select Tools->Link User-Compiled Model... from the menu.

The Link Model dialog box opens.

|                             | Link Model(s) to Simulator:2 |  |  |  |  |

|-----------------------------|------------------------------|--|--|--|--|

|                             | Link Status                  |  |  |  |  |

|                             |                              |  |  |  |  |

| Ш                           |                              |  |  |  |  |

| Ш                           |                              |  |  |  |  |

| Ē                           |                              |  |  |  |  |

| Link Simulator Link Options |                              |  |  |  |  |

|                             | Cancel                       |  |  |  |  |

Click the *Link Options...* button to open the Link Options dialog box. From this dialog, select the models to be linked from the left hand column (Object files in Project), and click the >> button to move them to the right hand column (*Object Files to be Linked*)

| -                                                                                            | Link Options                                          |

|----------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Active Projects<br>/hfs/godot/d1/projec                                                      | cts/Documentation_prj/net 🗵                           |

| Object Files in Project                                                                      | Object Files to be Linked                             |

| MyModel (circuit)<br>PNDIODE (circuit)<br>U2PA (circuit)<br>U2PB (circuit)<br>XLIN (circuit) | <pre>in_prj/networks/My Model &gt;&gt; &lt;&lt;</pre> |

| Select models to be linked                                                                   | Select models to be unlinked                          |

| ОК                                                                                           | Cancel Help                                           |

Click the *OK* button to close the dialog. Click the *Link Simulator* button to link the chosen models into a new executable. The new executable will be placed in the projects directory (if an existing executable was already there, it will be renamed).

# Managing Model Files

The Analog Model Development Kit interface uses several files as a means of managing the C-code and the compile and link process.

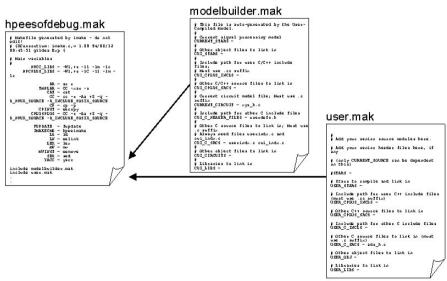

The program copies certain files from the *\$HPEESOF\_DIR/modelbuilder/lib* directory to the local project directory. For a model file called *MyModel*, when the *Create New Code Template* button is clicked the file *cui\_circuit.template* is copied to *MyModel.c.* When the *Compile* button is clicked, *hpeesofdebug.mak* or *hpeesofopt.mak* is always copied (depending on setting of *Debug* check box) and *userindx.c, user.mak* are copied if they are not there, and *MyModel\_h.c, cui\_indx.c, modelbuilder.mak* are created if they do not already exist, and existing files may be overwritten.

Figure 1-2. C-code File Relationship

The Makefile compiles the *MyModel\_h.c* file which is autogenerated when the *Compile* button is clicked and the file is out-of-date relative to dialog box settings. It includes the header files and the user's code.

During the compile process the Makefile sources the *hpeesofdebug.mak* (or *hpeesofopt.mak*) file. This file includes the autogenerated modelbuilder.mak file and the user-editable user.mak file. The Model Builder interface executes the make process; the user can manually build the program with the following command:

#### hpeesofmake -f hpeesofdebug.mak < target>

where *<target>* is one of the following:

| compile_only     | compile only the active model.                                                                    |

|------------------|---------------------------------------------------------------------------------------------------|

| link_only        | link without compiling anything.                                                                  |

| compile_and_link | compile the active file and link everything.                                                      |

| update_only      | compile the active and any out-of-date files (including those in <i>user.mak</i> ).               |

| update_and_link  | compile the active and any out-of-date files (including those in <i>user.mak</i> ) and then link. |

Figure 1-3. Makefile Relationship.

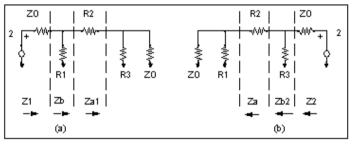

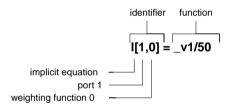

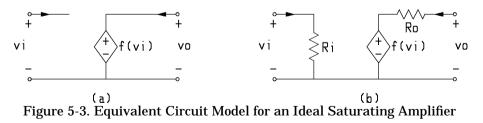

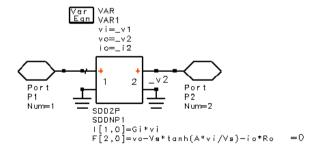

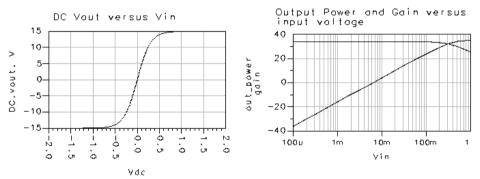

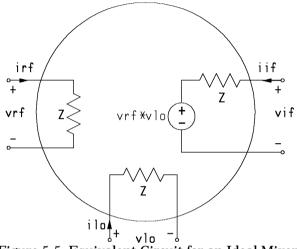

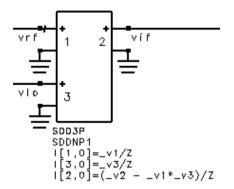

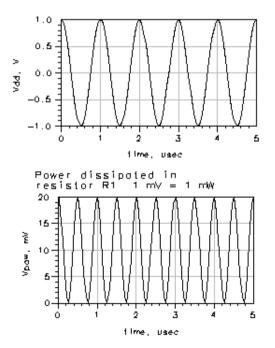

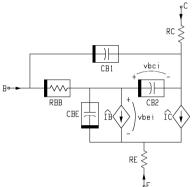

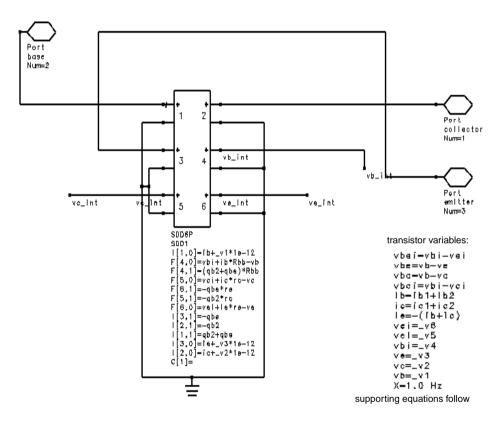

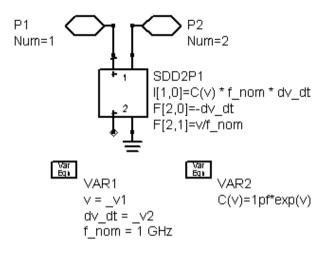

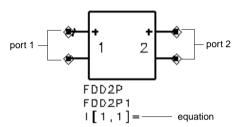

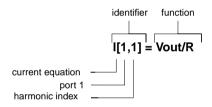

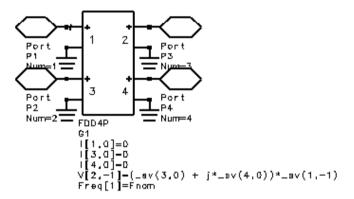

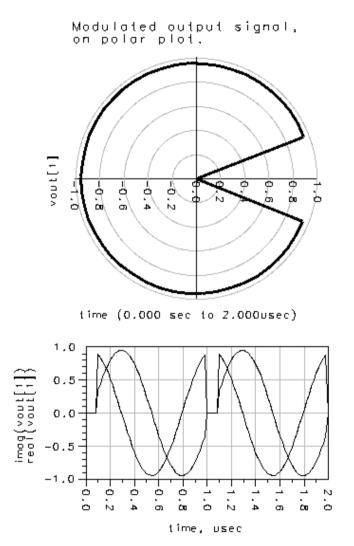

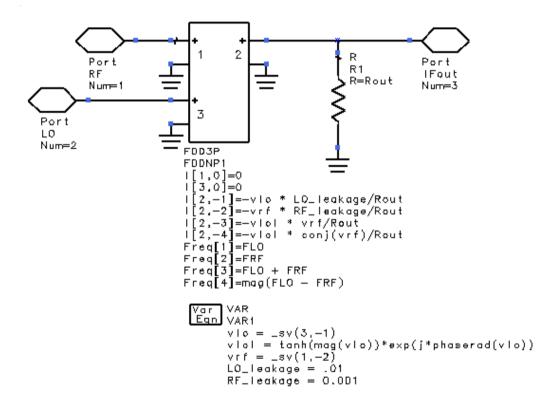

# Accessing Dynamically Loaded Devices